티스토리 뷰

논문 리뷰 - 0.64μm-pitch CMOS Image Sensor with Low Leakage Current of Vertical Transfer Gate

Image sensor 장인이 되고픈 공학도 2023. 4. 28. 14:342021년에 네이버 블로그에 포스팅한 글입니다.

ㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡ

픽셀 피치가 작아지면서 아래 그림과 같이 FD와 TG의거리 그리고 PD와 FD의 거리가 짧아지고 있다.

이로써 PD에서 VTG를 거치지 않고 바로 FD로 이동을 하는 현상이 나타나게되며 이로 인해 black으로 나와야 할 화면에 white가 나오는 defect가 발생하게 된다.

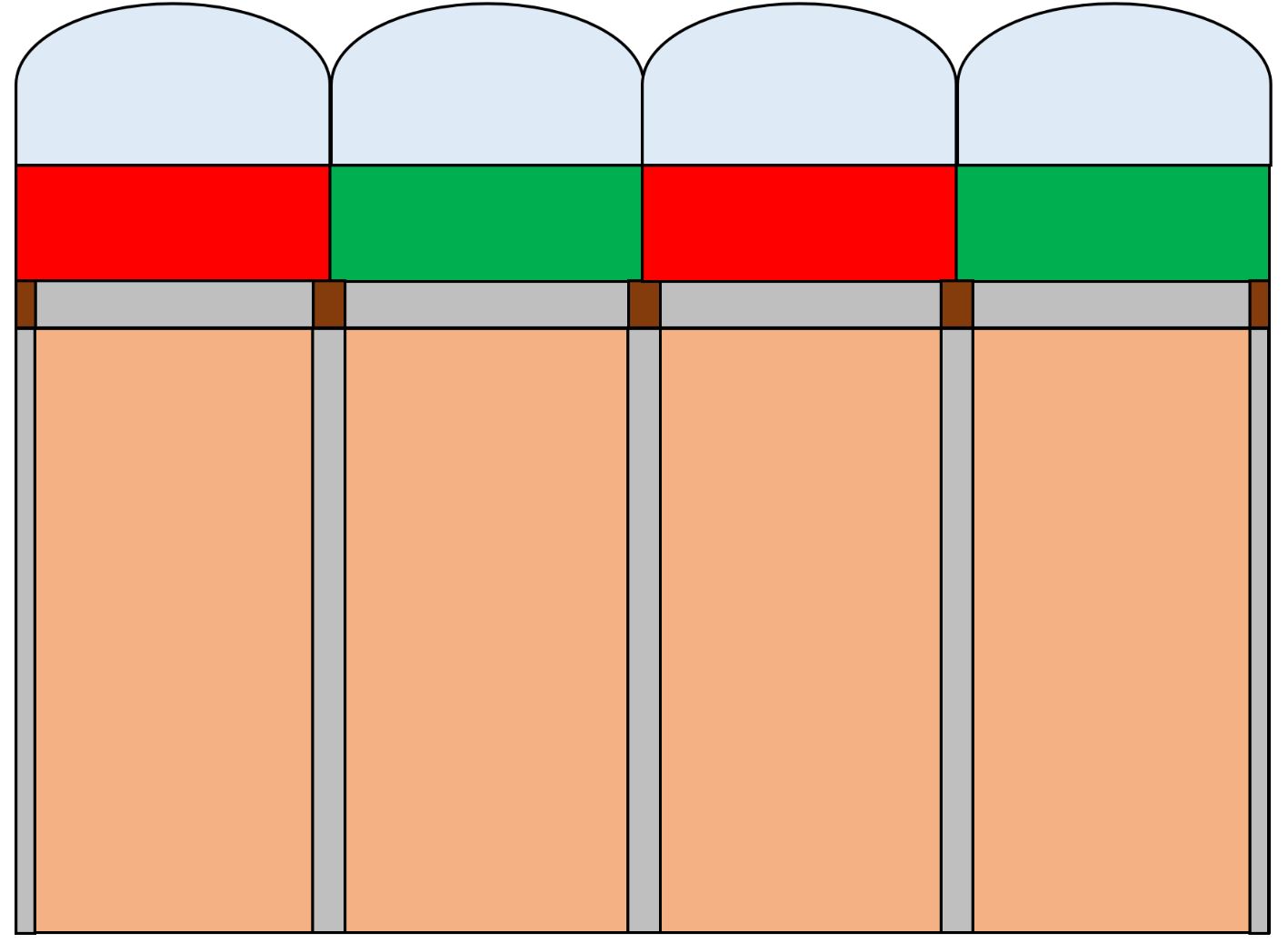

아래의 가장 왼쪽 그림을 보게되면, 현대 CIS는 기본적으로 4-T구조를 형성하고 있다. 이는 4개의 photodiode가 1개의 FD를 공유 하고 있다는 말이다.

따라서, 만약 4개의 PD중 1개에서 전자가 터널링 현상이든, impact ionization이든, GIDL(gate-induced drain leakage)이든 어떠한 이유로 전자가 FD쪽으로 들어가게되면, 아래의 정중앙에 위치한 그림과 같이, 공유된 4개의 PD에서 동일한 값의 defect이 발생하게 된다.

마지막 그림에서 볼 수 있듯이, FD와 TG(VTG)의 거리가 멀어질수록 N-bit WD 즉, 공유된 픽셀의 white defect가 눈에 띄게 줄어드는 것을 알 수 있다.

다음으로 Impact ionization과 GIDL에 대한 개념으로..... GIDL은 발표한지 오래되어 제대로 기억나지 않는다. 좀 더 빨리 리뷰를 작성하도록하자.

쨋든, Impact ionization에 대해 말하면, Drain에 높은 전압을 인가하게되면 Source에 있는 전자가 Drain으로 이동하게 된다.

전자가 drain으로 빠른속도로 이동하는 과정에서 Silicon의 격자, 그리고 전자들끼리 부딛히게 되면서 전자들은 사방으로 틩겨져 나가게 되고, 그로 인한 전류가 왼쪽 아래에 보이는것과 같이 발생하게 된다. 이는 당연히 원치않은 누설전류로 분류된다.

또한, 전자가 Oxide나 Gate의 표면에 불안전한 trap에 붙잡히게 되어 oxide에 붙잡히게 될 경우 성능 열화가 생기게되며, gate에 붙잡히게 될경우, 임계점으로 인가해야하는 Vg의 양이 높아지게 된다.

작은 픽셀 구조에서 성능을 열화시키는 이유에는 터널링이 좀 더 주된 이유라고 보는게 맞을 것 같다.

왼쪽에서부터 차례대로, 전압이 인가되어 있지 않으면 평형한 상태를 유지하다가, 전압을 인가하게되면 에너지 밴드가 휘게된다.

그리고 마지막 그림처럼 전압이 과하게 들어가게되면, valance band의 바로 옆에 conduction band가 위치하는 그림이 되어 밴드 갭이 충분히 크지 않다면, 터널링으로 슝슝 이동할 수 있게 된다. 이로 인해 원치않는 전자의 이동이 발생해 defect이 발생하게된다.

이러한 현상을 잡기위해, 그 중에서도 Impact ionization과 GIDL을 잡기위해 LDD등 Drain의 도핑농도 혹은 도핑 깊이를 작게하는 공정을 진행하게된다.

왼쪽은 일반적인 이온 임플란테이션으로 도핑이 정상적으로 깊게까지 된다, 반대로 LDD기법을 사용하게되면 실리콘 기판위에 보호막역할을 하게된 oxide를 깔고 이온폭격을 해줌으로서, 도핑이 좀 더 얕게 깔리게 된다.

이러한 공정으로, Drain에 전압을 인가해도 전자가 과도한 속도로 drain쪽으로 이동하지 않기 때문에, hot carrier effect등에 의한 열화는 줄일 수 있게된다. (pixel이 작을수록 drain과 source 사이가 짧기 때문에 drain에 도핑이 강할수록 더욱 강한 전계가 생성되어 치명적일것이라 생각된다.)

끝으로, 결과값을 비교한 그래프를 보게되면 FD의 도핑농도 즉, Drain의 도핑 프로파일에 따라 그래프 분포에 차이를 보이며, 도핑 프로파일이 작은 검정색으로 표현된 스플릿1(반대로 Cov = FD의 용량은 낮음)이 더욱 낮은 White Defect을 가지고 있음을 확인할 수 있다.

그리고 오른쪽 그래프를 확인하면, contact과 LDD의 도핑을 적고 약하게 만듦으로써(검정색 -아무런 공정 사용x, 검정색 - contact 농도 낮춤, ldd농도 낮춤), white defect또한 낮아짐을 확인할 수 있다.

여기서 하나의 질문거리는 FD에 도핑농도를 낮춤으로써 white defect을 낮춘다고 했다.

하지만 상식적으로 FD가 작아지게되면 FWC또한 작아지기 때문에 전하가 우물에 흘러 넘치는 현상 등으로 인한 defect이 발생할 수 있으며, 다이나믹 레인지도 줄어들 수 있다.

이에 반해, 그만큼 pixel ptich가 줄어들었고 photodiode의 크기도 줄어들었으므로, 이정도의 FD로 인한 FWC 감소는 문제 없다고 생각 할 수도있다.

결과가 어떤지는 직접 시뮬레이션과 칩을 제작해봐야 알 수 있겠지

'전공 > 논문 리뷰' 카테고리의 다른 글

| 논문 리뷰 - PDAF under NIR (0) | 2023.04.28 |

|---|---|

| 논문 리뷰 - 2022 ISSCC, 0.56 μm pixel (0) | 2023.04.28 |

| 논문 리뷰 - QE and Optical Cross-talk of Pixels with BST for Near-Infrared Imaging (0) | 2023.04.28 |

| 논문 리뷰 - VLSI 2021, CF Grid (0) | 2023.04.28 |

| 논문 리뷰 - ISSCC 2021 7.9, 0.64μm pixel (0) | 2023.04.28 |

- Total

- Today

- Yesterday

- Samsung

- ISOCELL HP2

- Tetra^2 픽셀

- channeling effect

- RTS noise

- 슈퍼 QPD

- PDAF

- image sensor

- Twisted PD

- reverse bias

- quad color filter array

- conversion gain

- temporal noise

- signal-to-noise ratio

- 한국광학회

- pxiel

- 4t

- DB hitek

- Auto-focusing

- ion implantation

- metamaterial

- pixel

- Auto focusing

- IISW 2019

- 이온 주입

- doping concentration

- SNR 10

- CIS

- Noise

- 1/f noise

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | |||

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 | 31 |